In questa sezione vogliamo affrontare il problema della lettura dei segnali provenienti da circuiti integrati di conversione e condizionamento ad esempio degli ADC ad alta velocità e nella direzione opposta, ovvero generati dallo ZYNQ e da inviare a periferiche esterne connesse al pinout della sezione FPGA.

Scarica schema frontend analogico differenziale e isolato dal campo ADC 18bit 2MSPS

Scarica il databook del chip THS4520 differential rail to rail low distortion AMP. OP.

Scarica progetto Eagle sch e pcb (attenzione connettore JAE non connesso)

Direzione Zynq -> FPGA -> periferiche. I segnali che costituiscono un dato, presenti in un registro caricato presumibilmente via AXI, siano da inviare ad un pin del GPIO dell’FPGA (modalità common mode) oppure a una coppia di pin del GPIO dell’FPGA (modalità LVDS ovvero differenziale).

In questo caso ci serve uno shift register ovvero un dispositivo che possa essere caricato in parallelo e scaricato in seriale, spingendo a seconda delle impostazioni il contenuto verso destra o verso sinistra. Ogni shift avverrà sincronizzato sul fronte di un segnale di clock in modo da poter rilevare correttamente la presenza del dato sul booleano in output.

Se consideriamo dal punto di vista hardware lo sift register come un insieme di Flip Flop avremo le seguenti funzion/pin da descrivere in VHDL.

- clock

- serial input

- asynchronus set/rest

- synchronus set/reset

- synchronus o asynchronus caricamento parallelo

- clock enable

- uscita seriale o parallela.

L’uscita dello shift register potrà essere settata in una dei seguenti modi:

- seriale: solo il contenuto dell’ultimo flip flop viene collegato al resto del circuito restituendo un booleano.

- parallela: Il contenuto dei un numeor maggiore di 1 dei flip flop sono accessibili, di solito quelli dell’estensione necessaria ad esempio 18bit dei 32 disponibili nella word perché questa è la misura della conversione di un ADC ad esso collegato.

- shift modes: verso destra o verso sinistra.

Esistono molte maniere per descrivere in VHDL uno shift register ma quella più intuitiva è tramite l’uso di un ciclo for.

entity shift_reg is Port( data_in : in STD_LOGIC_VECTOR (31 downto 0); clk : in STD_LOGIC; serial_out : out STD_LOGIC); end shift_reg; architetctural Behavioral of shift_reg is for i in 0 to 6 loop shreg(i+1) <= shreg(i); end loop; shreg(0) <= SI;

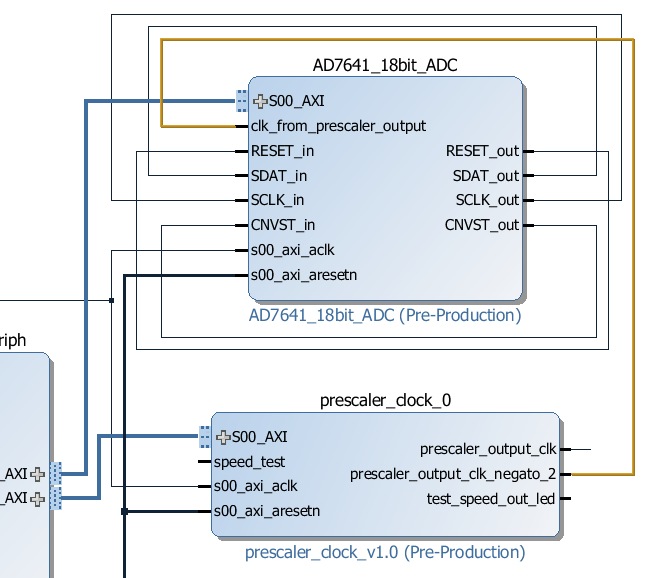

Scarica, dal link sottostante, un design di test della velocità e affidabilità della serializzazione e de serializzazione. I segnali e i registri dell’IP sono cortocircuitati ovvero l’uscita viene riportata in ingresso sincronizzando la velocità con l’IP prescaler prodotto negli esempi precedenti. La velocità del prescaler è impostata da terminale Linux su un registro AXI. viene restituito il dato deserializzato. Si spinga in alto la frequenza fino a che il dato serializzate-> deserializzato rimane leggibile.

Download tet serializzatore de serialiazzatore -> AD7641_18_bit_ADC

Serializzatore su evento.

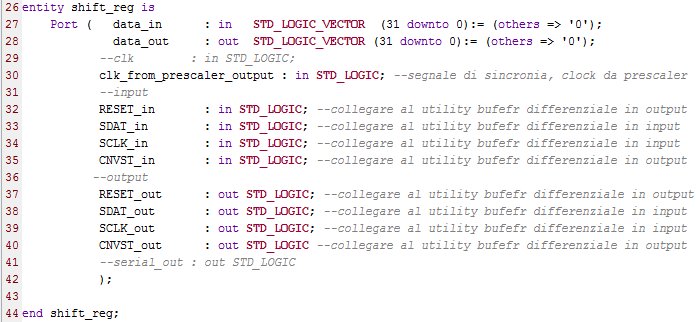

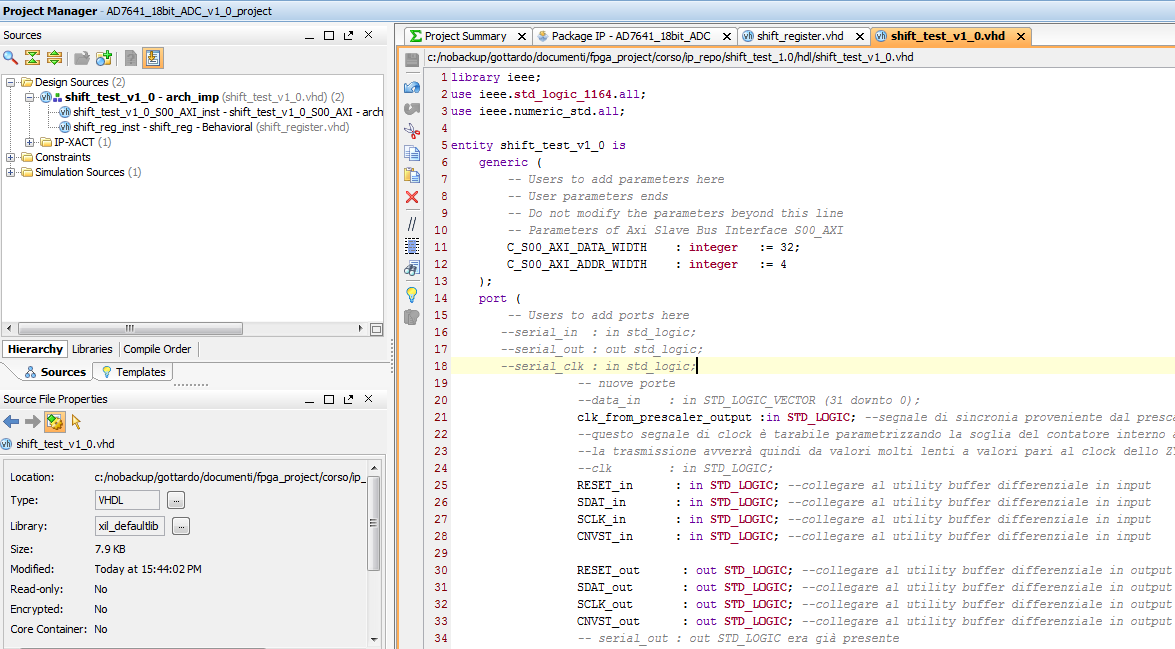

Consideriamo l’IP mostrato sopra in cui l’avanzamento del bit nel registro serializzatore sia delegato non a un ciclo for bensì al fronte di uno stimolo dovuto al presentarsi di un segnale in un pin hardware. Questà è la soluzione più ovvia da implementare in ambito FPGA. Nell’immagine la definizione delle porte nell’entity:

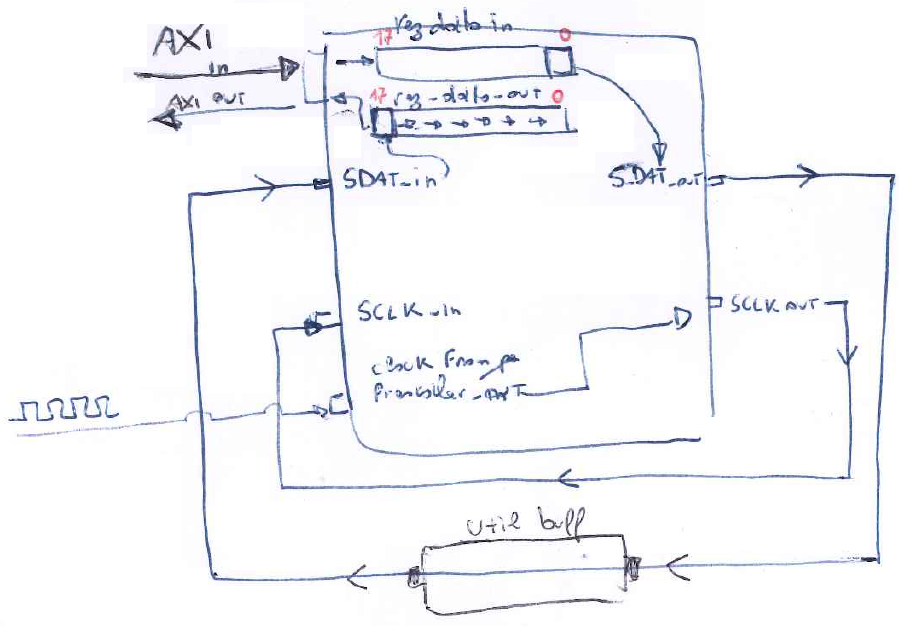

Le porte sono duplicate in input e output perché si intende caricare un dato via AXI, serializzarlo, inviarlo allo stesso IP in una porta di ingresso, parallelizzarlo e reinviarlo via AXI al terminale. Lo scopo è quello di testare la massima velocità con cui il dato originariamente inviato in AXI possa tornare senza perdita di informazione al terminale che lo ha caricato dopo il processo di serializzazione e de serializzazione. Nell’immagine il principio di funzionamento.

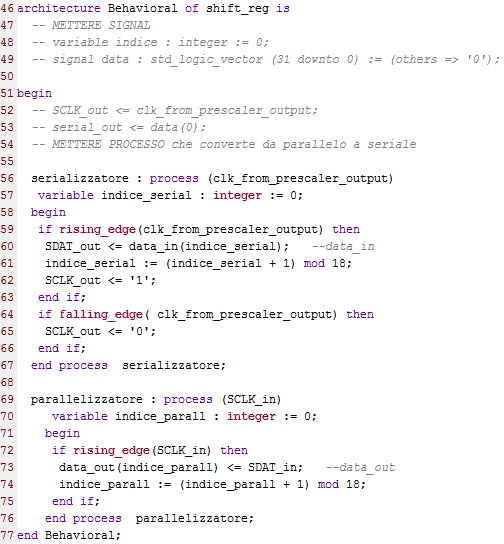

la serializzazione su evento sarà sensibile a rising_edge del segnale proveniente dal clock come mostrato sotto.

Per quanto riguarda i sorgenti del top module, nell’architettura dovrà comparire la stessa definizione delle porte usate nel sorgente del behaviural.

right click to enlarge.

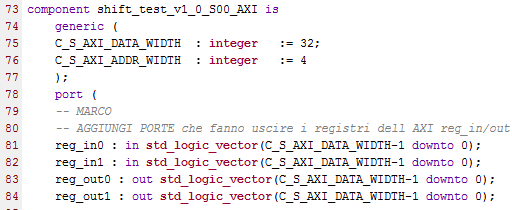

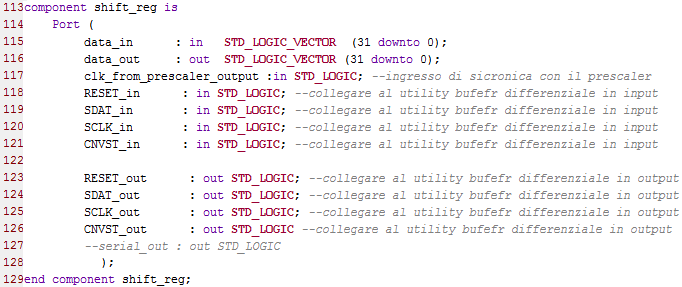

Nell’area di definizione dei “component” del top module, compaiono i registri di ingresso e uscita con cui il nostro IP comunica tramite AXI con il resto dell’architettura e con il mondo esterno alla scheda.

e quindi l’stanza del component shift_reg:

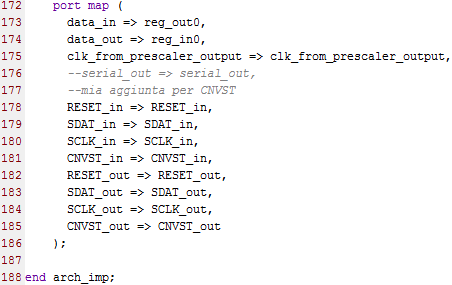

nella sezione port map( …) aggiungeremo:

reg_in0 => reg_in0,

reg_in1 => reg_in1,

reg_out0 => reg_out0,

reg_out1 => reg_out1

Ora si aggiunge l’istanza che descrive i collegamenti dei segnali delle nuove porte.

Come interfacciare il chip AD7641 allo ZYNQ 7000.

Scarica da questo link una breve descrizione su come implementare il protocollo di comunicazione tra la sezione FPGA dello ZYNQ e il connettore JAE del modulo portoghese con AD7641 e chip di interfaccia SN65LVDT.

Come interfacciare il moduloanalogico Portoghese

Quando si procede al collegamento del vero chip ADC hardware risulta necessario scollegare il segnale di clock autogenerato nel block design tramite l’IP del prescaler e mettersi in acquisizione di questo da una coppia di pin differenziali.

Ecco una prima bozza del design -> AD7641fullView

I pin esterni saranno collegati secondo questa configurazione ->Make_expernal_Table

Visita la pagina per acquistare questo libro -> FPGA to high speed Adc data acquisition